TMS320C6678ACYPA Multicore Fix/Float Pt Dig Sig Proc

♠ Product Description

| Product Attribute | Attribute Value |

| Manufacturer: | Texas Instruments |

| Product Category: | Digital Signal Processors & Controllers - DSP, DSC |

| Product: | DSPs |

| Series: | TMS320C6678 |

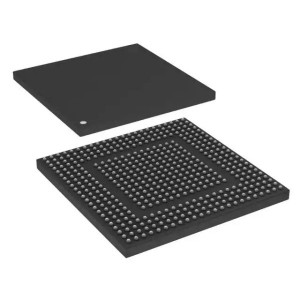

| Mounting Style: | SMD/SMT |

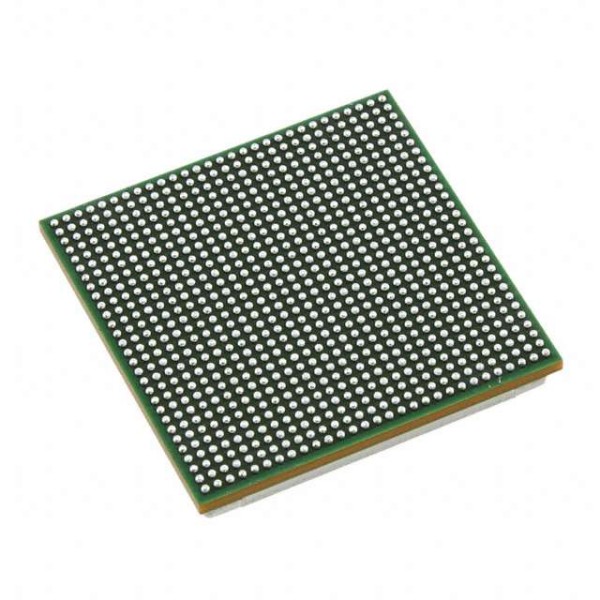

| Package / Case: | FCBGA-841 |

| Core: | C66x |

| Number of Cores: | 8 Core |

| Maximum Clock Frequency: | 1 GHz, 1.25 GHz |

| L1 Cache Instruction Memory: | 8 x 32 kB |

| L1 Cache Data Memory: | 8 x 32 kB |

| Program Memory Size: | - |

| Data RAM Size: | - |

| Operating Supply Voltage: | 900 mV to 1.1 V |

| Minimum Operating Temperature: | - 40 C |

| Maximum Operating Temperature: | + 100 C |

| Packaging: | Tray |

| Brand: | Texas Instruments |

| Data Bus Width: | 8 bit/16 bit/32 bit |

| Instruction Type: | Fixed/Floating Point |

| MMACS: | 320000 MMACS |

| Moisture Sensitive: | Yes |

| Number of I/Os: | 16 I/O |

| Number of Timers/Counters: | 16 Timer |

| Product Type: | DSP - Digital Signal Processors & Controllers |

| Factory Pack Quantity: | 44 |

| Subcategory: | Embedded Processors & Controllers |

| Supply Voltage - Max: | 1.1 V |

| Supply Voltage - Min: | 900 mV |

| Unit Weight: | 0.252724 oz |

♠ Multicore Fixed and Floating-Point Digital Signal Processor

The TMS320C6678 DSP is a highest-performance fixed/floating-point DSP that is based on TI's KeyStone multicore architecture. Incorporating the new and innovative C66x DSP core, this device can run at a core speed of up to 1.4 GHz. For developers of a broad range of applications, such as mission-critical systems, edical imaging, test and automation, and other applications requiring high performance, TI's TMS320C6678 DSP offers 11.2 GHz cumulative DSP and enables a platform that is power-efficient and easy to use. In addition, it is fully backward compatible with all existing C6000 family fixed and floating point DSPs.

TI's KeyStone architecture provides a programmable platform integrating various subsystems (C66x cores, memory subsystem, peripherals, and accelerators) and uses several innovative components and techniques to maximize intra-device and inter-device communication that allows the various DSP resources to operate efficiently and seamlessly. Central to this architecture are key components such as Multicore Navigator that allows for efficient data management between the various device components. The TeraNet is a non-blocking switch fabric enabling fast and contention-free internal data movement. The multicore shared memory controller allows access to shared and external memory directly without drawing from switch fabric capacity.

• Eight TMS320C66x™ DSP Core Subsystems (C66x CorePacs), Each with

– 1.0 GHz, 1.25 GHz, or 1.4 GHz C66x Fixed/Floating-Point CPU Core

› 44.8 GMAC/Core for Fixed Point @ 1.4 GHz

› 22.4 GFLOP/Core for Floating Point @ 1.4 GHz

– Memory

› 32K Byte L1P Per Core

› 32K Byte L1D Per Core

› 512K Byte Local L2 Per Core

• Multicore Shared Memory Controller (MSMC)

– 4096KB MSM SRAM Memory Shared by Eight DSP C66x CorePacs

– Memory Protection Unit for Both MSM SRAM and DDR3_EMIF

• Multicore Navigator

– 8192 Multipurpose Hardware Queues with Queue Manager

– Packet-Based DMA for Zero-Overhead Transfers

• Network Coprocessor

– Packet Accelerator Enables Support for

› Transport Plane IPsec, GTP-U, SCTP, PDCP

› L2 User Plane PDCP (RoHC, Air Ciphering)

› 1-Gbps Wire-Speed Throughput at 1.5 MPackets Per Second

– Security Accelerator Engine Enables Support for

› IPSec, SRTP, 3GPP, WiMAX Air Interface, and SSL/TLS Security

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (256-bit Hash), MD5

› Up to 2.8 Gbps Encryption Speed

• Peripherals

– Four Lanes of SRIO 2.1

› 1.24/2.5/3.125/5 GBaud Operation Supported Per Lane

› Supports Direct I/O, Message Passing

› Supports Four 1×, Two 2×, One 4×, and Two 1× + One 2× Link Configurations

– PCIe Gen2

› Single Port Supporting 1 or 2 Lanes

› Supports Up To 5 GBaud Per Lane

– HyperLink

› Supports Connections to Other KeyStone Architecture Devices Providing Resource Scalability

› Supports up to 50 Gbaud

– Gigabit Ethernet (GbE) Switch Subsystem

› Two SGMII Ports

› Supports 10/100/1000 Mbps Operation

– 64-Bit DDR3 Interface (DDR3-1600)

› 8G Byte Addressable Memory Space

– 16-Bit EMIF

– Two Telecom Serial Ports (TSIP)

› Supports 1024 DS0s Per TSIP

› Supports 2/4/8 Lanes at 32.768/16.384/8.192 Mbps Per Lane

– UART Interface

– I2

C Interface

– 16 GPIO Pins

– SPI Interface

– Semaphore Module

– Sixteen 64-Bit Timers

– Three On-Chip PLLs

• Commercial Temperature:

– 0°C to 85°C

• Extended Temperature:

– -40°C to 100°C

• Mission-Critical Systems

• High-Performance Computing Systems

• Communications

• Audio

• Video Infrastructure

• Imaging

• Analytics

• Networking

• Media Processing

• Industrial Automation

• Automation and Process Control